完整性

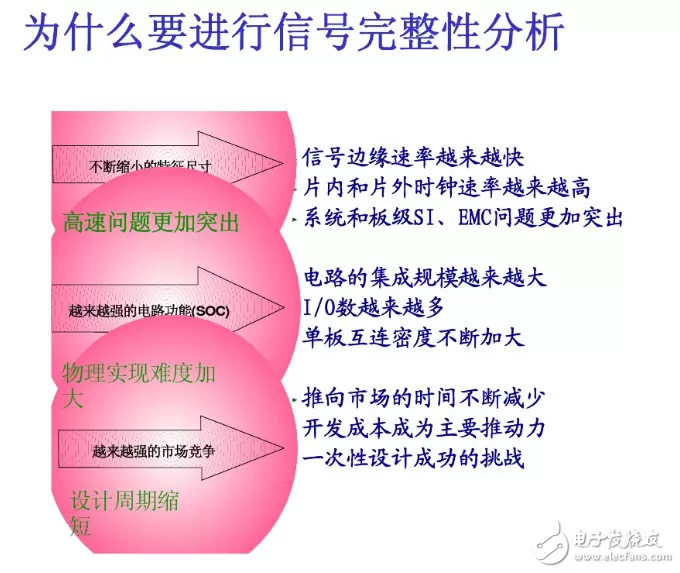

信号完整性是指信号在传输路径上的质量,由于路径的特性对信号造成的失真。数字电路刚出现的时候,由于传输信号速率很低,在电路分析时采用低频和直流的方法就可以。

但是随着数字信号频率越来越高,电路的模拟特性越来越显现出来,所以也有人说信号完整性是数字与模拟的桥梁。数字电路工程师已经需要大量的射频和微波电路基础理论来分析数字电路。高端的信号完整性试验室都需要同时配备示波器和网络分析仪。

传输路径可以是普通的金属线,可以是光学器件,也可以是其他媒质。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一单一因素导致的,而是系统中多种因素共同引起的。

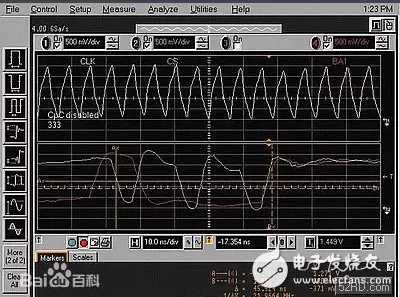

不管是在系统中什么地方,隔离并排除信号完整性故障总是一项极具挑战性的任务。您需要高带宽而且省时的解决方案来正确解决高速信号偏差问题,信号完整性测试设备数字示波器、逻辑分析仪、实时频谱分析仪、时域反射计解决方案、信号发生器、高保真探头和分析软件。

信号完整性分析概论

高速领域:时钟频率超过100MHz或者Tr小于1ns,信号完整性效应就变得重要。通常将这种情况称之为高频领域或高速领域。

体会:可作为经验法则。大致判断某块电路是否需要进行计算或仿真。对于低于此频率以下,Tr以上的,便可采用大致的经验来设计。对于低频唯一的要求就是联通即可。高一点的要求便是美观工整。按要求设计呗,不用考虑太多SI问题。做好PDS即可了。

信号完整性三种影响和后果:

1.时序;2.噪声;3.电磁干扰。

理解:具体产生以上问题还没有细致研究过。待成为半神再来解释

SI特定噪声源:

1.单一网络的信号完整性;在信号路径或返回路径上由于阻抗突变而引起的反射与失真

2.两个或多个网络间的串扰;和理想回路与非理想回路耦合的互容互感。

3.电源和地分配中的轨道塌陷;在电源、地网络中的电压变化!

4.来自整个系统的电磁干扰和辐射。

体会:单一网络包括从源端,源内阻,传输线,接收端容抗,返回路径。保持信号完整性,就需要尽可能将以上设计成相同阻抗。如果接收与发送不匹配就需要采用T型网络或者π型网络进行阻抗匹配。比如视频信号采用的特殊阻抗为75欧姆,电路板采用的是50欧姆,其便可使用衰减电路来匹配特性阻抗。

任何改变横截面或网络几何形状的特性都会改变信号所受到的特性阻抗。使信号所感受到的阻抗突变如下:

1.线宽的变化;2.层转换;3、返回路径平面上的间隙;4.接插件5.分支线,T型线或者桩线;6.网络末端。

体会:需要注意的是网络末端和接插件,网络末端可以端接一个匹配同阻抗的电阻(引出问题为消耗额外功率,以及减少电流。电阻并接在网络中,存在一个问题即电压为源端电压减去传输线分压。电流为源电流减去各个分支电流。如果源端为电流驱动类型,则有可能导致接收端灌电流太小,驱动不了)接插件可以并接一个电容至地。)

定义:突变—令阻抗发生变化的所有特征称之为突变。

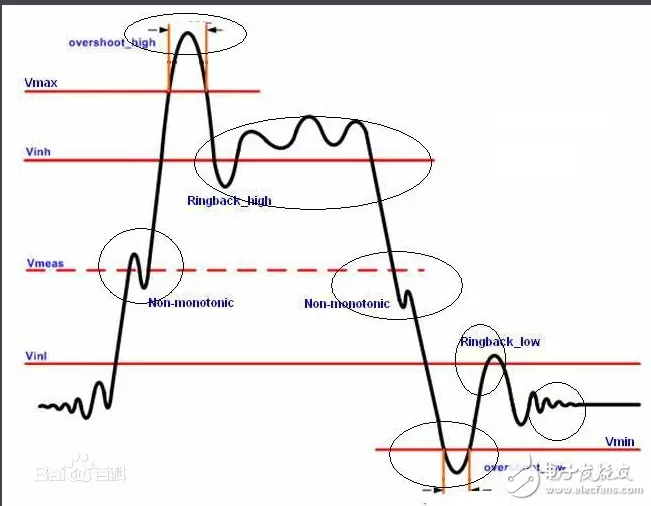

振铃:通常认为是因为阻抗突变造成的反射引起的振铃。

1.如果把人比喻成信号,道路比喻成传输线,坑洼看做特征阻抗

---当人迈大步子(信号的上升时间》信号往返时间),道路上的的坑洼会被跳过,感觉不到,走的很顺畅;当人迈着小碎步(信号的上升时间《信号往返时间),道路上的坑洼则不可避免的,这时走时会遇到很大阻力

---当不考虑外界干扰,如果道路保持一致(瞬态阻抗),人(信号)在道路上会保持恒定不变,如果道路出现坑洼(阻抗变化,中途遇到的电阻,电容,电感,过孔,PCB转角,接插件),人(信号)在道路上速度就会发生改变(反射)

1.大多数高速数字系统中,信号上升时间约是时钟周期的10%,即1/10x1/Fclock。例如100MHZ使中的上升时间大约是1NS.

2.在FR4板材上铜线条中信号速度为6in/ns(=15cm/ns)。

3.传输线的特征阻抗,只有当信号在走线上的往返时间大于信号的上升时间才考虑。

3.所有与信号完整性噪声问题有关的效应都应与下面四类特定噪声源中的一个:

(1)单一网络的信号完整性;

在信号路径或返回路径上由于阻抗突变而引起的反射与失真。使信号感受到阻抗变化的情况。例如振铃问题就是由于信号传输过程中感受到阻抗的变化,发生的信号反射

(2)两个或多个网络间的串扰;

产生串扰的原因:正是网络间的容性耦合和感性耦合,给有害噪声从一个网络到达另一个网络提供了路径

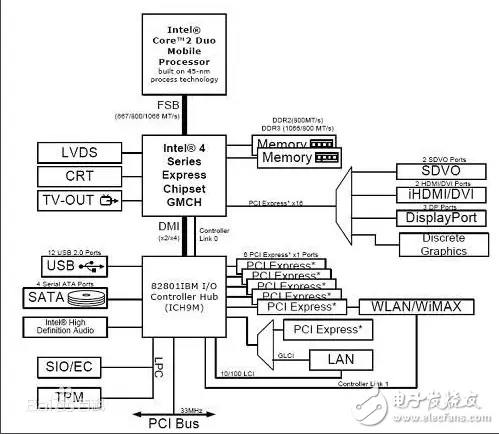

(3)电源和地分配中的轨道塌陷(旁路和去耦)---电感引起

当通过电源和地路径的电流发生变化时,在电源路径和地路径间的阻抗上将产生一个压降。这个压降就意味着供给芯片的电压减小了,可以看做是电源与地间的电压减小或塌陷。这就是为啥要在芯片电源旁加个电容原因

电感--由于电流变化产生的感应电压引起传输线效应,突变,串扰,开关噪声,轨道塌陷,地弹和大大多数电磁干扰源(EMI)

(4)来自整个系统的电磁干扰和辐射。